Aggiungi ai preferiti

Vedi traduzione automatica

Questa è una traduzione automatica. Per vedere il testo originale in inglese

cliccare qui

#Tendenze

{{{sourceTextContent.title}}}

L'adattatore di PCIe2RasPI ospita le schede di ingresso/uscita del lampone pi su una mini scanalatura di PCIe.

{{{sourceTextContent.subTitle}}}

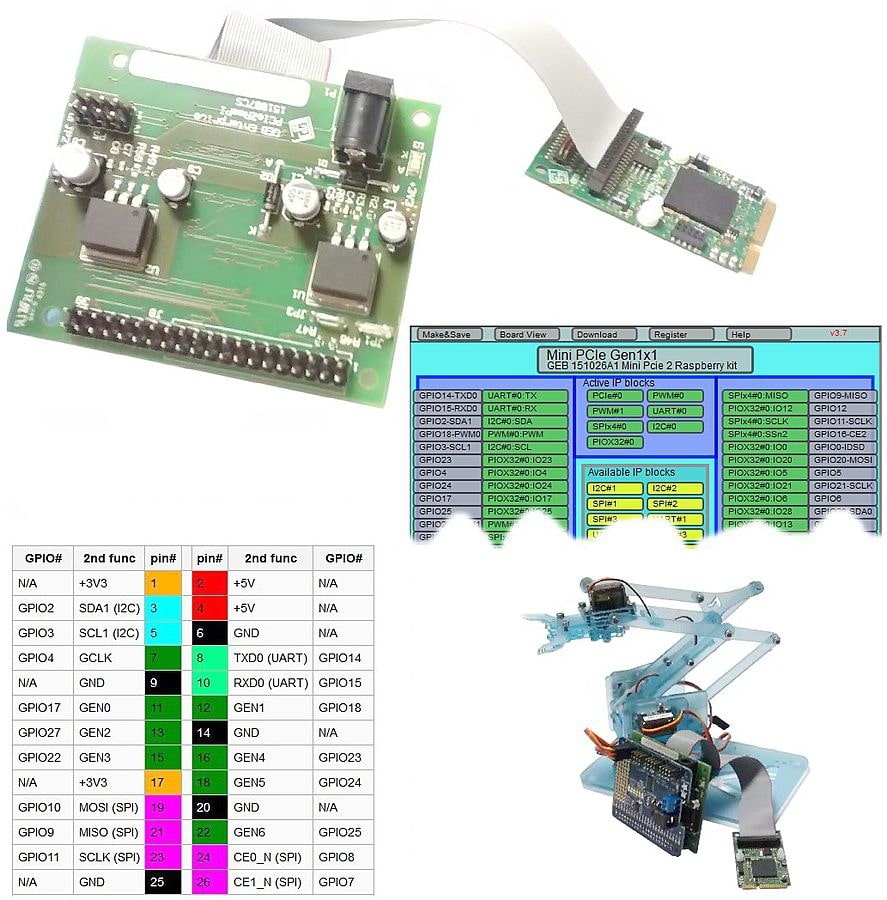

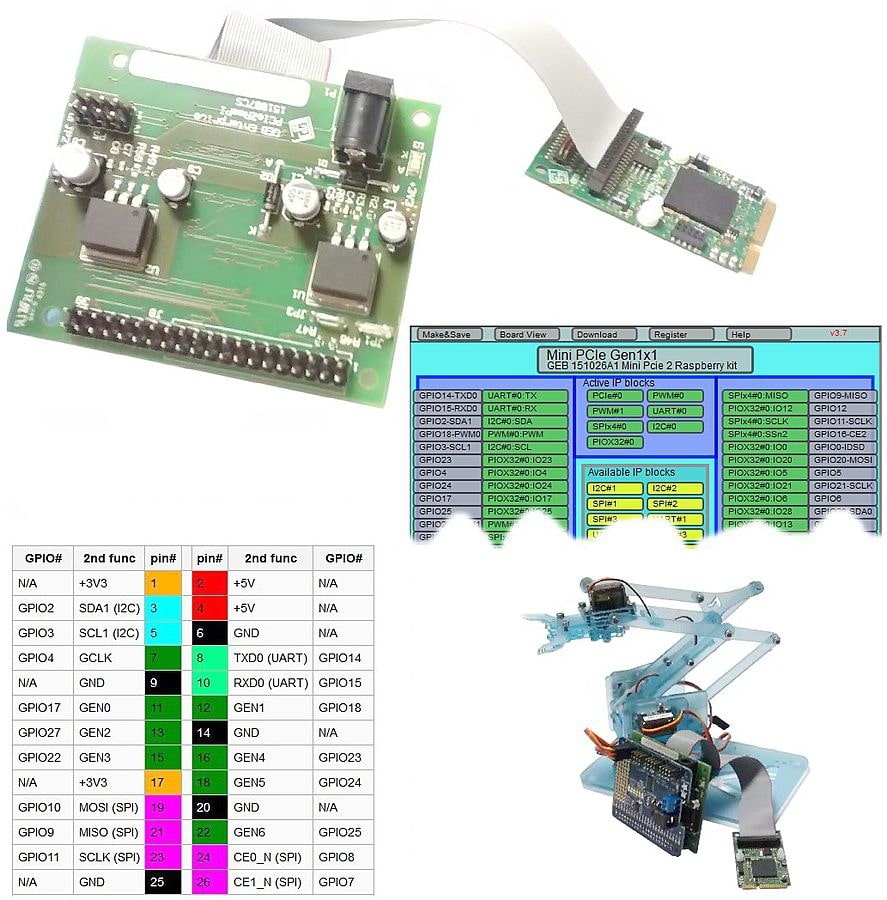

Roma, impresa di GEB sta trasportando l'adattatore di PCIe2RasPI rendendo in grado le schede madri incastonate di PCIE per ospitare tutti i bordi dell'ingresso/uscita del lampone

{{{sourceTextContent.description}}}

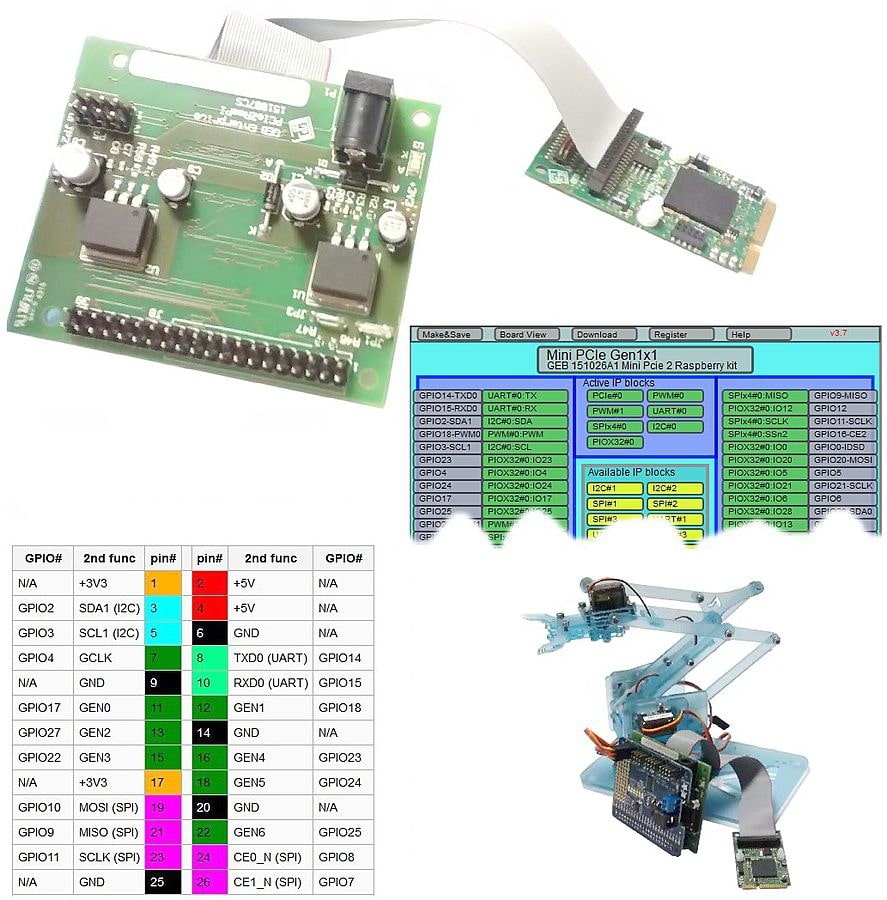

L'adattatore di PCIe2RasPI, collegato sul mini connettore dell'ingresso/uscita di PCIe e i FPGA programmabili rendono disponibile la stessa funzione dei perni disponibile sul lampone e su più…. i perni disponibili dei supplementi possono essere utilizzati per dare la funzionalità e la velocità che non possono essere raggiunte con l'esecuzione del software sul CPU del lampone.

Realmente quando una mini carta di PCIE Fpga è stata collegata ad una scheda madre incastonata del PC, aggiunge possibilità programmabile dell'ingresso/uscita e di DSP di larghezza di banda di FPGA l'alta ad un basso costo, rendentegli l'ideale per le apparecchiature in molti campi dell'applicazione, quali electromedical, automazione, i giocatori di dati ed i registratori ecc.

Molte applicazioni possono essere sviluppate per mezzo degli attrezzi dell'attrezzo di FEWE (redattore di fotoricettore facile di Fpga) GEB liberamente che sta venendo presto. Sta permettendo che gli utenti adattassero per possedere l'applicazione a partire da una certa mascherina generata da GEB usando un web browser, senza qualunque altro attrezzo.

Inoltre le mascherine prestabilite dall'utente possono essere ottenute usando la mascherina relativa

Il soddisfare di Fpga può essere sviluppato anche per mezzo degli attrezzi tradizionali di Quartus o chiedendo un adattamento ad impresa di GEB. I corredi relativi di sviluppo rendono disponibile tutti di che abbiate bisogno per sviluppare sia il disegno di Fpga sotto Altera QSYS che il programma di applicazione usando i driver forniti di Linux o di Microsoft Windows.

Il PCIEM-15-IO ospita un ciclone IV GX EP4CGX30BF14C6N FPGA e due connettori dell'ingresso/uscita che mettono in evidenza 53 perni compiacenti dell'ingresso/uscita FPGA di LVTTL ed anche un segnale di Altera di 3 orologi che può essere usato per connettere le applicazioni sincrone.

Il FPGA ha un'interfaccia di arrivo di PCI Express PCIe x1 GEN1, permettendo che il PC trar massimo vantaggio dai perni dell'ingresso/uscita di FPGA. I perni dell'ingresso/uscita possono anche essere controllati da un regolatore di DMA di rendimento elevato, in grado di trasferire fino a 250 MBYTE/sec una volta utilizzati in pieno duplex